## **Digital DC/DC PMBus 10A Power Module**

#### **ZL9010M**

The <code>ZL9010M</code> is a 10A adjustable output, step-down synchronous PMBus-compliant digital power supply. Included in the module is a high-performance digital PWM controller, power MOSFETs, an inductor and all the passive components required for a highly integrated DC/DC power solution. This power module has built-in auto compensation algorithms, which eliminates the need for manual compensation design work. The ZL9010M operates over a wide input voltage range and supports an output voltage range of 0.6V to 3.6V, which can be set by external resistors or via PMBus. Only bulk input and output capacitors are needed to finish the design. The output voltage can be precisely regulated to as low as 0.6V with  $\pm 1\%$  output voltage regulation over line, load and temperature variations.

The ZL9010M functions as a switch mode power supply with added benefits of auto compensation, programmable power management features, parametric monitoring and status reporting capabilities.

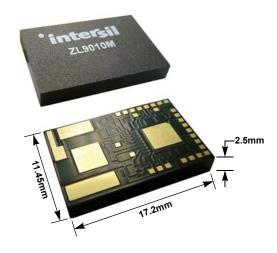

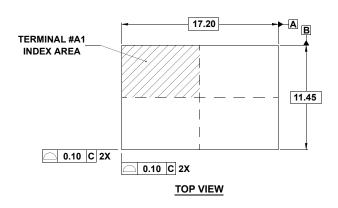

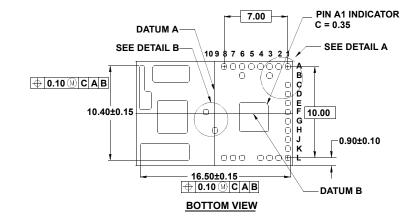

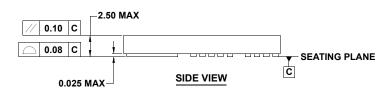

The ZL9010M is packaged in a thermally enhanced, compact (17.2mm x 11.45mm) and low profile (2.5mm) overmolded high-density array (HDA) package module suitable for automated assembly by standard surface mount equipment. The ZL9010M is RoHS compliant.

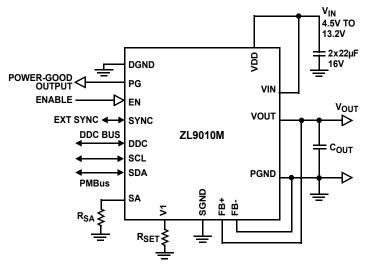

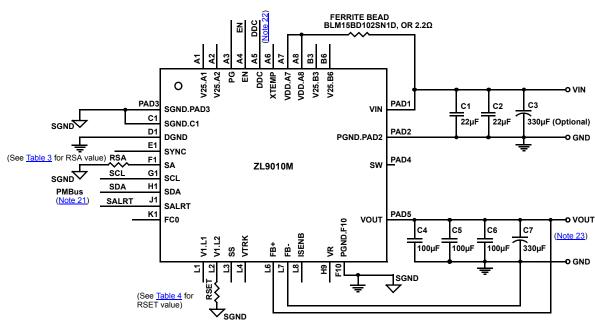

Figure 1 represents a typical implementation of the ZL9010M. For PMBus operation, it is recommended to tie the Enable pin (EN) to SGND.

#### **Features**

- · Complete digital switch mode power supply

- Auto compensating PID filter

- ±1% output voltage accuracy

- · External synchronization

- · Overcurrent/undercurrent protection

- · Output voltage tracking

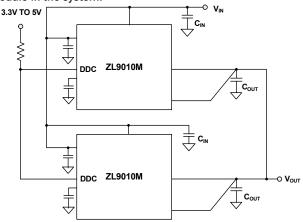

- · Current sharing and phase interleaving

- · Programmable sequencing (delay and ramp time)

- Snapshot™ parametric capture

- · PMBus compliant

### **Applications**

- · Server, telecom and datacom

- · Industrial and medical equipment

- · General purpose point-of-load

#### **Related Literature**

AN2034, "Configuring Current Sharing on the ZL2004 and ZL2006"

FIGURE 1. TYPICAL APPLICATION CIRCUIT

\*Patent pending package

FIGURE 2. SMALL FOOTPRINT PACKAGE WITH LOW PROFILE AT 2.5mm

## **Table of Contents**

|    | n Configuration                                           |      |

|----|-----------------------------------------------------------|------|

| Pi | n Descriptions                                            | 4    |

| Pi | nout Internal Circuit                                     | 6    |

| O: | dering Information                                        | 7    |

| ΑI | solute Maximum Ratings                                    | 8    |

| Th | ermal Information                                         | 8    |

| R  | ecommended Operating Conditions                           | 8    |

| ΕI | ectrical Specifications                                   | 8    |

|    | pical Performance Curves                                  |      |

| _  | erating Curves                                            |      |

|    | plication Information                                     |      |

|    | Internal Bias and Input Voltage Considerations            |      |

|    | Design Trade-Offs with Switching Frequency                | . 14 |

|    | Selection of the Input Capacitor                          |      |

| F. | nctional Description                                      |      |

|    | Multi-Mode Pins                                           |      |

|    | PMBus Communications                                      |      |

|    | PMBus Module Address Selection.                           |      |

|    | Phase Spreading for a Single-Phase Mode of Operation      |      |

|    | Start-Up Procedure                                        | . 17 |

|    | Soft-Start Delay and Ramp Times                           |      |

|    | Power-Good                                                |      |

|    | Loop Compensation                                         | . 20 |

|    | Adaptive Diode Emulation                                  |      |

|    | Input Undervoltage Lockout                                |      |

|    | Output Prebias Protection                                 | . 21 |

|    | Output Overcurrent Protection                             |      |

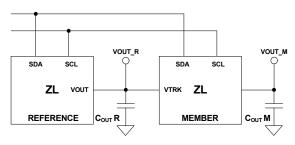

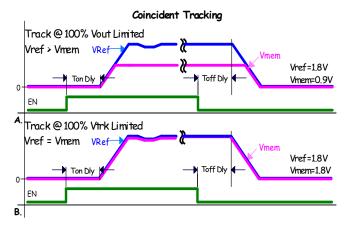

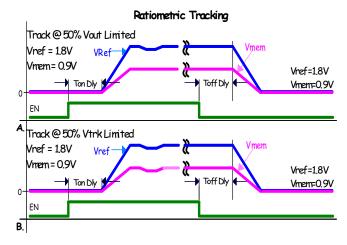

|    | Voltage Tracking                                          |      |

|    | Tracking Groups                                           | . 24 |

|    | Voltage Margining                                         |      |

|    | Output Sequencing                                         |      |

|    | Fault Spreading                                           |      |

|    | Active Current Sharing                                    |      |

|    | Temperature Monitoring Using the XTEMP Pin                |      |

|    | SnapShot Parameter Capture                                |      |

|    | Nonvolatile Memory and Device Security Featuresyout Guide |      |

|    |                                                           |      |

| Th | ermal Considerations                                      |      |

|    | Package Description                                       |      |

|    | Thermal Vias                                              | . 28 |

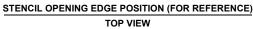

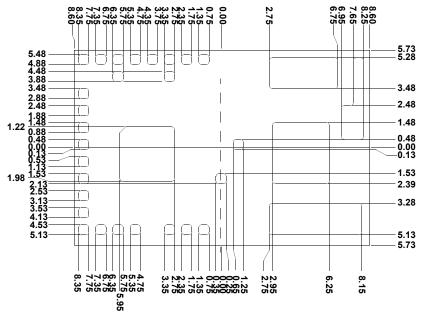

|    | Stencil Pattern Design                                    |      |

| D: | /Bus Command Summary                                      |      |

| -1 | PMBus™ Data Formats                                       |      |

| ΡI | /Bus Use Guidelines                                       |      |

|    | Summary                                                   |      |

| ΡI | /Bus Commands Description                                 |      |

|    |                                                           |      |

| Firmware Revision History | 67 |

|---------------------------|----|

| Revision History          | 68 |

| About Intersil            | 68 |

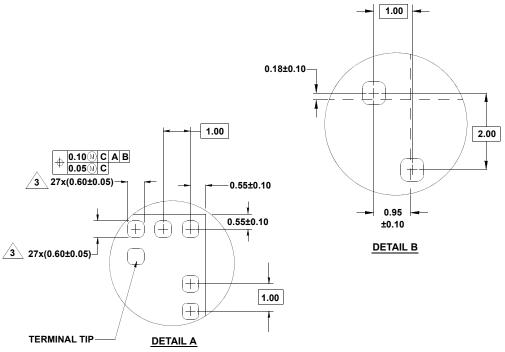

| Package Outline Drawing   | 69 |

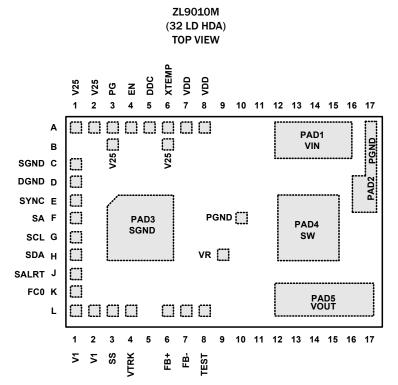

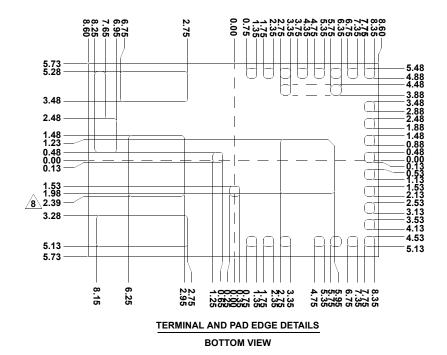

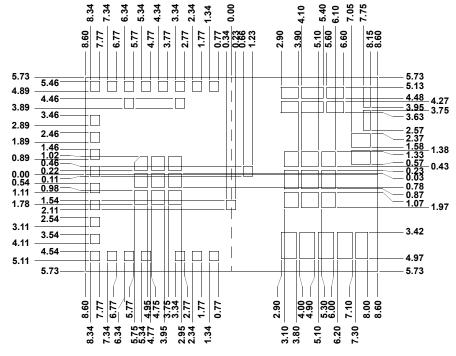

## **Pin Configuration**

### **Pin Descriptions**

| PIN               | LABEL | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                       |

|-------------------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, A2,<br>B3, B6 | V25   | PWR  | Internal 2.5V reference. It is used to power internal circuitry.                                                                                                                                                                                                                                                  |

| А3                | PG    | 0    | Power-good output. Provide open-drain power-good signal. By default, the PG pin asserts if the output is within +15/-10% of the target voltage. These limits and the polarity of the pin may be changed via the PMBus interface.                                                                                  |

| A4                | EN    | I    | Enable input. This pin is factory set as active high. Pull-up to enable the module switching and pull-down to disable switching. If the module is controlled through PMBus command, tie a $10 \text{k}\Omega$ resistor from this pin to SGND to avoid this pin floating.                                          |

| A5                | DDC   | I/O  | Digital-DC bus (open drain). The DDC pin on all Digital modules in one application should be connected together. This dedicated bus provides the communication channel between modules for features such as sequencing, fault spreading and current sharing. A pull-up resistor is required for this application. |

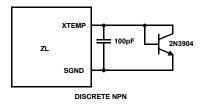

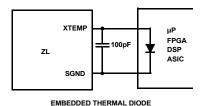

| А6                | XTEMP | I    | External temperature sensor input. Connect to an external 2N3904 transistor with a diode configuration. See Figure 26 on page 26.                                                                                                                                                                                 |

| A7, A8            | VDD   | PWR  | Controller input voltage. Tie to VIN directly.                                                                                                                                                                                                                                                                    |

| C1                | SGND  | PWR  | Signal ground. Connect to low impedance ground plane. Refer to "Layout Guide" on page 27.                                                                                                                                                                                                                         |

| D1                | DGND  | PWR  | Digital ground. Common return for digital signals. Connect to low impedance ground plane. Refer to "Layout Guide" on page 27.                                                                                                                                                                                     |

| E1                | SYNC  | I/O  | Clock synchronization. Used for synchronization to external frequency reference. See <u>Table 8</u> for setting switching frequency.                                                                                                                                                                              |

| F1                | SA    | I    | Serial address select pin. Used to assign unique PMBus address to each module and phase spreading.                                                                                                                                                                                                                |

| F10               | PGND  | PWR  | Power ground. Connect to low impedance ground plane.                                                                                                                                                                                                                                                              |

| G1                | SCL   | I/O  | Serial clock. PMBus interface pin.                                                                                                                                                                                                                                                                                |

| H1                | SDA   | I/O  | Serial data. PMBus interface pin.                                                                                                                                                                                                                                                                                 |

| Н9                | VR    | PWR  | Internal 5V reference. Used to power internal drivers. The current limit for the VR pin is 10mA. Please consider this when using the VR pin for driving external circuitry.                                                                                                                                       |

Submit Document Feedback 4 intersil FN8422.3 March 16, 2016

# Pin Descriptions (Continued)

| PIN    | LABEL                                                                                                                                                                                                                                                                                                                                                                   | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J1     | SALRT                                                                                                                                                                                                                                                                                                                                                                   | 0    | Serial alert. PMBus interface pin.                                                                                                                                                                                                                                                                                                                                                                                                       |

| K1     | FC0                                                                                                                                                                                                                                                                                                                                                                     | I    | Mode Setting. Used to set the single-phase/current sharing mode, auto compensation and SYNC configuration. See Table 9 on page 20.                                                                                                                                                                                                                                                                                                       |

| L1, L2 | V1                                                                                                                                                                                                                                                                                                                                                                      | I    | Output voltage selection pin. It is used to program the output voltage through pin-strap setting or connecting a resistor from the V1 pin to SGND (see <u>Table 4 "SINGLE RESISTOR VOUT SETTING" on page 17)</u> . The set voltage on this pin is the maximum allowed output voltage in PMBus programming.                                                                                                                               |

| L3     | SS I Soft-start pin. Set SS pin by pin-strapping or connecting a resistor to SGND using the appropriate resistor program the delay from when EN is asserted until the output voltage starts to ramp, the output voltage raturn on/off and input undervoltage lockout (UVLO) level (see <a href="Table 6 on page 18">Table 6 on page 18</a> ). This pin can also set tra |      | Soft-start pin. Set SS pin by pin-strapping or connecting a resistor to SGND using the appropriate resistor. The pin can program the delay from when EN is asserted until the output voltage starts to ramp, the output voltage ramp time during turn on/off and input undervoltage lockout (UVLO) level (see <u>Table 6 on page 18</u> ). This pin can also set tracking ratio and upper track limit (see <u>Table 10 on page 23</u> ). |

| L4     | VTRK                                                                                                                                                                                                                                                                                                                                                                    | I    | Tracking sense input. Used to track an external voltage source.                                                                                                                                                                                                                                                                                                                                                                          |

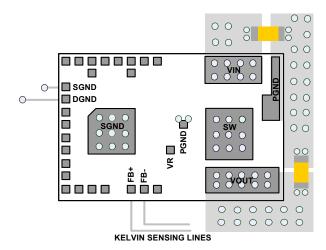

| L6     | FB+                                                                                                                                                                                                                                                                                                                                                                     | I    | Output voltage positive feedback. Positive inputs of differential remote sense for the regulator. Connect to the output rail or the regulation point of load/processor. This pin is noise sensitive. Refer to "Layout Guide" on page 27.                                                                                                                                                                                                 |

| L7     | FB-                                                                                                                                                                                                                                                                                                                                                                     | I    | Output voltage negative feedback. Negative input of the differential remote sense for the regulator. Connect to the negative rail or ground of the load/processor.                                                                                                                                                                                                                                                                       |

| L8     | TEST                                                                                                                                                                                                                                                                                                                                                                    | TEST | Test pin. For factory test use. Solder down the pin for mechanical strength, but do not connect the pin.                                                                                                                                                                                                                                                                                                                                 |

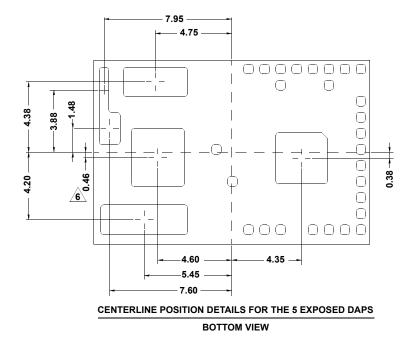

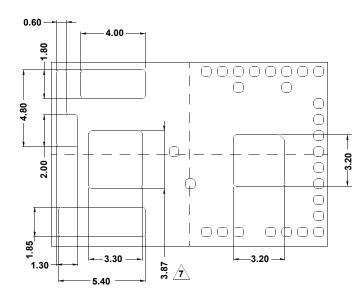

| PAD1   | VIN                                                                                                                                                                                                                                                                                                                                                                     | PWR  | Power inputs. Input voltage range: 4.5V to 13.2V. Tie directly to the input rail. When the input is between 4.5V to 5.5V, VIN should be tied directly to VCC.                                                                                                                                                                                                                                                                            |

| PAD2   | PGND                                                                                                                                                                                                                                                                                                                                                                    | PWR  | Power ground. Power ground pins for both input and output returns.                                                                                                                                                                                                                                                                                                                                                                       |

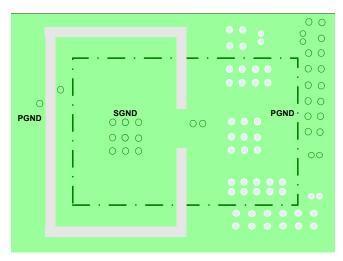

| PAD3   | SGND                                                                                                                                                                                                                                                                                                                                                                    | PWR  | Signal ground. Connect to low impedance ground plane (see Figure 27 on page 28).                                                                                                                                                                                                                                                                                                                                                         |

| PAD4   | sw                                                                                                                                                                                                                                                                                                                                                                      | PWR  | Switch node. Use for monitoring switching frequency. SW pad should be floating or used for snubber connections. To achieve better thermal performance, the SW planes can also be used for heat removal with thermal vias connected to large inner layers (see Figure 27 on page 28).                                                                                                                                                     |

| PAD5   | VOUT                                                                                                                                                                                                                                                                                                                                                                    | PWR  | Power Output. Apply output load between these pins and PGND pins. Output voltage range: 0.6V to 3.6V.                                                                                                                                                                                                                                                                                                                                    |

Submit Document Feedback 5 intersil 5 FN8422.3 March 16, 2016

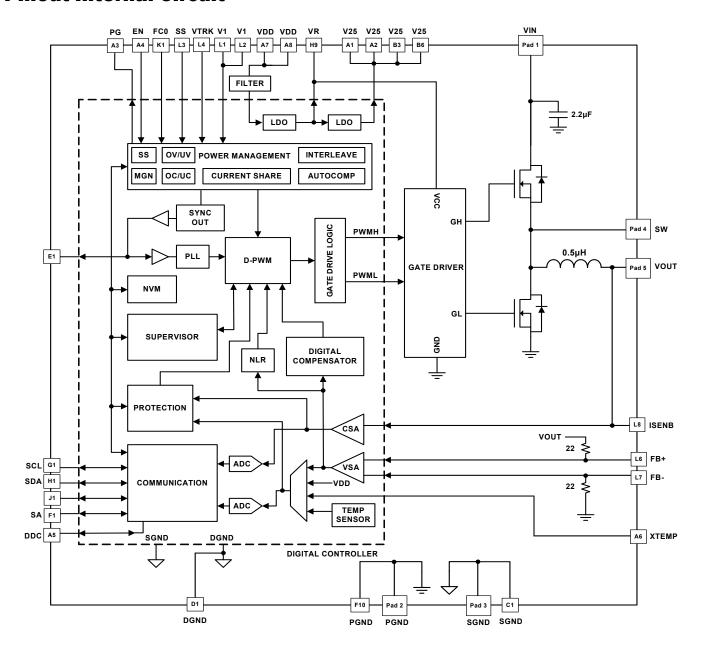

### **Pinout Internal Circuit**

Submit Document Feedback 6 intersil FN8422.3 March 16, 2016

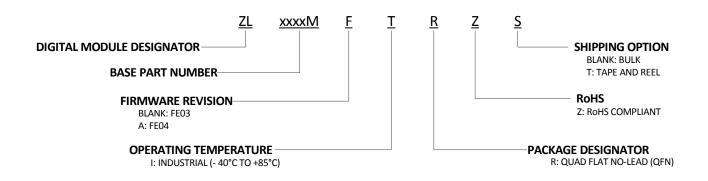

### **Ordering Information**

| PART NUMBER<br>(Notes 1, 2, 3) | PART<br>MARKING | FIRMWARE REVISION (Note 4) | TEMP RANGE<br>(°C) | PACKAGE<br>(RoHS Compliant) | PKG.<br>DWG. # |  |

|--------------------------------|-----------------|----------------------------|--------------------|-----------------------------|----------------|--|

| ZL9010MIRZ                     | ZL9010M         | FE03                       | -40 to +85         | 32 Ld 17.2x11.45 HDA        | Y32.17.2x11.45 |  |

| ZL9010MAIRZ                    | ZL9010M         | FE04                       | -40 to +85         | 32 Ld 17.2x11.45 HDA        | Y32.17.2x11.45 |  |

| ZL9010MEVAL1Z Evaluation Board |                 |                            |                    |                             |                |  |

#### NOTES:

- 1. Add "-T\*" suffix for tape and reel. Please refer to TB347 for details on reel specifications.

- These Intersil plastic packaged products are RoHS compliant by EU exemption 7C-I and employ special Pb-free material sets, molding compounds/die

attach materials, and 100% matte tin plate plus anneal (e3) termination finish which is compatible with both SnPb and Pb-free soldering operations.

Intersil RoHS compliant products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC

J STD-020.

- 3. For Moisture Sensitivity Level (MSL), please see device information page for <u>ZL9010M</u>. For more information on MSL please see Tech Brief <u>TB363</u>.

- 4. See "Firmware Revision History" on page 67; only the latest firmware revision is recommended for new designs.

Submit Document Feedback 7 intersil FN8422.3 March 16, 2016

#### Absolute Maximum Ratings (Note 5)

| _                                                      |

|--------------------------------------------------------|

| DC Supply Voltage for VDD Pin0.3V to 17V               |

| Input Voltage for VIN Pin0.3V to 17V                   |

| MOSFET Drive Reference for VR Pin0.3V to 6.5V          |

| 2.5V Logic Reference for V25 Pin0.3V to 3V             |

| Logic I/O Voltage for PG, EN, DDC, SYNC,               |

| PG, SCL, SDA, SALRT, FCO, V1, SS Pins0.3V to 6V        |

| Analog Input Voltages XTEMP, VTRK,                     |

| FB+, FB-, ISENB Pins0.3V to 6V                         |

| Switch Node for SW Pin                                 |

| Continuous(PGND - 0.3V) to 30V                         |

| Transient (<100ns) (PGND - 5V) to 30V                  |

| Ground Voltage Differential (DGND - SGND, PGND - SGND) |

| for DGND, SGND and PGND Pins0.3V to +0.3V              |

| ESD Rating                                             |

| Human Body Model (Tested per JESD22-A114F)2000V        |

| Machine Model (Tested per JESD22-A115C)200V            |

| Charged Device Model (Tested per JESD22-C110D) 1000V   |

| Latch-up (Tested per JESD78C; Class 2, Level A)        |

|                                                        |

#### **Thermal Information**

| Thermal Resistance (Typical)   | $\theta_{JA}$ (°C/W) | $\theta_{JC}$ (°C/W) |

|--------------------------------|----------------------|----------------------|

| 32 Ld HDA Package (Notes 8, 9) | 15                   | 1                    |

| Storage Temperature            |                      | 5°C to +150°C        |

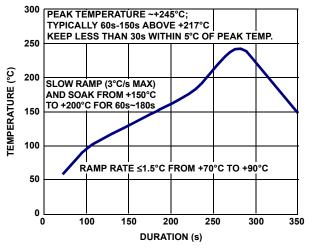

| Pb-Free Reflow Profile         |                      | .see Figure 28       |

#### **Recommended Operating Conditions**

| Input Supply Voltage Range, V <sub>IN</sub>           | 4.5V to 13.2V |

|-------------------------------------------------------|---------------|

| Input Supply For Controller, V <sub>DD</sub> (Note 6) | 4.5V to 13.2V |

| Driver Supply Voltage, VR                             | 4.5V to 5.5V  |

| Output Voltage Range, V <sub>OUT</sub> (Note 7)       | 0.54V to 3.6V |

| Output Current Range, I <sub>OUT(DC)</sub> (Note 20)  | 0A to 10A     |

| Operating Junction Temperature Range, T <sub>J</sub>  |               |

|                                                       |               |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 5. Voltage measured with respect to SGND.

- 6.  $V_{IN}$  supplies the power FETs.  $V_{DD}$  supplies the controller.  $V_{IN}$  can be tied to  $V_{DD}$ . For  $V_{DD} \le 5.5V$ ,  $V_{DD}$  should be tied to VR.

- 7. Includes ±10% margin limits.

- 8. θ<sub>JA</sub> is simulated in free air with device mounted on a four-layer FR-4 test board (76.2 x 114.3 x 1.6mm) with 80% coverage, 2oz Cu on top and bottom layers, plus two, buried, one-ounce Cu layers with coverage across the entire test board area. Multiple vias were used, with via diameter = 0.3mm on 1.2mm pitch.

- 9. For  $\theta_{\mbox{\scriptsize JC}}\!,$  the "case" temperature is measured at the center of the package underside.

# **Electrical Specifications** $V_{IN} = V_{DD} = 12V$ , $T_A = -40$ °C to +85°C, unless otherwise noted. Typical values are at $T_A = +25$ °C. **Boldface** limits apply across the operating temperature range, -40°C to +85°C.

| PARAMETER                                                                | TEST CONDITIONS                                                                                  | MIN<br>( <u>Note 10</u> ) | TYP<br>(Note 11) | MAX<br>(Note 10) | UNITS |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------|------------------|------------------|-------|

| INPUT AND SUPPLY CHARACTERISTICS                                         |                                                                                                  | ,                         |                  |                  |       |

| Input Bias Supply Current, I <sub>DD</sub>                               | V <sub>IN</sub> = V <sub>DD</sub> = 13.2V, f <sub>SW</sub> = 400kHz, no load                     | -                         | 35               | 45               | mA    |

| Input Bias Shutdown Current, I <sub>DDS</sub>                            | EN = 0V, no PMBus activity                                                                       | -                         | 15.5             | 20               | mA    |

| Input Supply Current, I <sub>VIN</sub>                                   | V <sub>IN</sub> = 12V, I <sub>OUT</sub> = 10A, V <sub>OUT</sub> = 1.2V, f <sub>SW</sub> = 400kHz | -                         | 1.22             | -                | Α     |

| VR Reference Output Voltage ( <u>Note 12</u> )                           | V <sub>DD</sub> > 6V                                                                             | 4.5                       | 5.2              | 5.7              | ٧     |

| V25 Reference Output Voltage (Note 12)                                   | V <sub>R</sub> > 3V                                                                              | 2.25                      | 2.5              | 2.75             | ٧     |

| OUTPUT CHARACTERISTICS                                                   |                                                                                                  | 1                         |                  |                  |       |

| Output Voltage Adjustment Range (Note 12)                                | V <sub>IN</sub> > V <sub>OUT</sub> . Does not include margin limits.                             | 0.6                       | -                | 3.3              | ٧     |

| Output Voltage Set-point Resolution                                      | Set using resistors. (See <u>Table 1</u> )                                                       | -                         | 50 - 200         | -                | m۷    |

|                                                                          | Set using PMBus with temperature compensation applied                                            | -                         | ±0.025           | -                | % FS  |

| Output Voltage Accuracy (Notes 12, 13)                                   | Includes line, load, temperature                                                                 | -1                        | -                | 1                | %     |

| VSEN Input Bias Current (Note 12)                                        | VSEN = 5.5V                                                                                      | -                         | 110              | 200              | μΑ    |

| Output Load Current (Note 20)                                            | V <sub>IN</sub> = 12V, V <sub>OUT</sub> = 1.2V                                                   | -                         | 10               | -                | Α     |

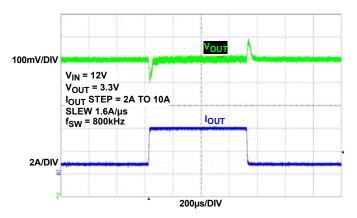

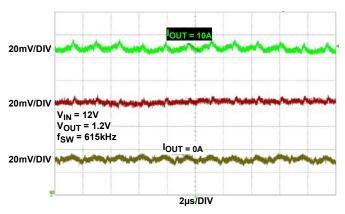

| Peak-to-peak Output Ripple Voltage, ΔV <sub>OUT</sub> ( <u>Note 13</u> ) | I <sub>OUT</sub> = 6A, V <sub>OUT</sub> = 1.2V, C <sub>OUT</sub> = 1000μF                        | -                         | 20               | _                | mV    |

| Soft-start Delay Duration Range (Notes 12, 14)                           | Set using SS pin or resistor                                                                     | 5                         | -                | 20               | ms    |

|                                                                          | Set using PMBus                                                                                  | 0.005                     | -                | 500              | s     |

Submit Document Feedback 8 Intersil FN8422.3 March 16, 2016

**Electrical Specifications**  $V_{IN} = V_{DD} = 12V$ ,  $T_A = -40\,^{\circ}$ C to  $+85\,^{\circ}$ C, unless otherwise noted. Typical values are at  $T_A = +25\,^{\circ}$ C. **Boldface** limits apply across the operating temperature range,  $-40\,^{\circ}$ C to  $+85\,^{\circ}$ C. (Continued)

| PARAMETER                                         | TEST CONDITIONS                                                              | MIN<br>(Note 10) | TYP<br>(Note 11) | MAX<br>(Note 10) | UNITS              |

|---------------------------------------------------|------------------------------------------------------------------------------|------------------|------------------|------------------|--------------------|

| Soft-start Delay Duration Accuracy (Notes 12, 14) | Turn-on delay (Note 16)                                                      | -                | -0.25/+4         | -                | ms                 |

|                                                   | Turn-off delay (Note 16)                                                     | -                | -0.25/+4         | -                | ms                 |

| Soft-start Ramp Duration Range (Notes 12, 14)     | Set using SS pin or resistor                                                 | 2                | -                | 20               | ms                 |

|                                                   | Set using                                                                    | 0                | -                | 200              | ms                 |

| Soft-start Ramp Duration Accuracy (Note 12)       |                                                                              | -                | 100              | -                | μs                 |

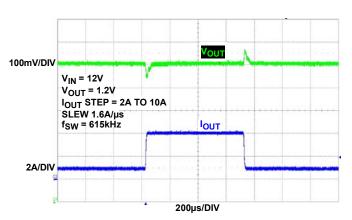

| DYNAMIC CHARACTERISTICS                           |                                                                              | -                | 11               |                  |                    |

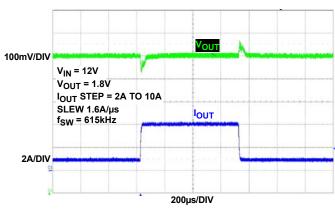

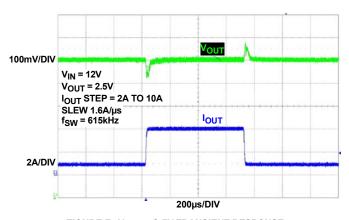

| Voltage Change for Positive Load Step             | $I_{OUT}$ = 2A to 10A, slew rate = 1.6A/µs, $V_{OUT}$ = 1.2V (see Figure 19) | -                | 4                | -                | %                  |

| Voltage Change for Positive Load Step             | $I_{OUT}$ = 10A to 2A, slew rate = 1.6A/µs, $V_{OUT}$ = 1.2V (see Figure 19) | -                | 4                | -                | %                  |

| OSCILLATOR AND SWITCHING CHARACTERISTICS          | (Note 12)                                                                    | 11               | 1.               |                  |                    |

| Switching Frequency Range                         |                                                                              | 300              | -                | 1000             | kHz                |

| Switching Frequency Set-point Accuracy            | Predefined settings (See <u>Table 1</u> )                                    | -5               | -                | 5                | %                  |

| Maximum PWM Duty Cycle                            | Factory setting (Note 19)                                                    | -                | -                | 95               | %                  |

| Minimum SYNC Pulse Width                          |                                                                              | 150              | -                | -                | ns                 |

| Input Clock Frequency Drift Tolerance             | External clock source                                                        | -13              | -                | 13               | %                  |

| LOGIC INPUT/OUTPUT CHARACTERISTICS (Note 12       | 2)                                                                           |                  | I.               | I                |                    |

| PMBus Speed                                       |                                                                              | _                | 100              | -                | kHz                |

| Logic Input Bias Current                          | EN, PG, SCL, SDA pins                                                        | -10              | -                | 10               | μΑ                 |

| Logic Input Low, V <sub>IL</sub>                  |                                                                              | -                | -                | 0.8              | V                  |

| Logic Input High, V <sub>IH</sub>                 |                                                                              | 2.0              | -                | -                | ٧                  |

| Logic Output Low, V <sub>OL</sub>                 | I <sub>OL</sub> ≤ 4mA ( <u>Note 18</u> )                                     | -                | -                | 0.4              | ٧                  |

| Logic Output High, V <sub>OH</sub>                | I <sub>OH</sub> ≥ -2mA ( <u>Note 18</u> )                                    | 2.25             | -                | -                | V                  |

| TRACKING (Note 12)                                |                                                                              | -                | 11               |                  |                    |

| VTRK Input Bias Current                           | VTRK = 5.5V                                                                  | -                | 110              | 200              | μΑ                 |

| VTRK Tracking Ramp Accuracy                       | 100% tracking, V <sub>OUT</sub> - VTRK, no prebias                           | -100             | -                | + 100            | m۷                 |

| VTRK Regulation Accuracy                          | 100% tracking, V <sub>OUT</sub> - VTRK                                       | -1               | -                | 1                | %                  |

| FAULT PROTECTION CHARACTERISTICS (Note 12)        |                                                                              |                  | I                | l .              |                    |

| UVLO Threshold Range                              | Configurable via PMBus                                                       | 2.85             | -                | 16               | ٧                  |

| UVLO Set-point Accuracy                           |                                                                              | -150             | -                | 150              | mV                 |

| UVLO Hysteresis                                   | Factory setting                                                              | -                | 3                | -                | %                  |

|                                                   | Configurable via I PMBus                                                     | 0                | -                | 100              | %                  |

| UVLO Delay                                        |                                                                              | -                | -                | 2.5              | μs                 |

| Power-Good V <sub>OUT</sub> Threshold             | Factory setting                                                              | -                | 90               | -                | % V <sub>OUT</sub> |

| Power-Good V <sub>OUT</sub> Hysteresis            | Factory setting                                                              | -                | 5                | -                | %                  |

| Power-Good Delay (Note 17)                        | Configurable via PMBus                                                       | 0                | -                | 500              | s                  |

| VSEN Undervoltage Threshold                       | Factory setting                                                              | -                | 85               | -                | % V <sub>OUT</sub> |

|                                                   | Configurable via PMBus                                                       | 0                | _                | 110              | % V <sub>OUT</sub> |

Submit Document Feedback 9 intersil FN8422.3 March 16, 2016

**Electrical Specifications**  $V_{IN} = V_{DD} = 12V$ ,  $T_A = -40 \,^{\circ}$ C to  $+85 \,^{\circ}$ C, unless otherwise noted. Typical values are at  $T_A = +25 \,^{\circ}$ C. **Boldface** limits apply across the operating temperature range, -40  $\,^{\circ}$ C to  $+85 \,^{\circ}$ C. (Continued)

| PARAMETER                                    | TEST CONDITIONS        | MIN<br>(Note 10) | TYP<br>( <u>Note 11</u> ) | MAX<br>(Note 10) | UNITS              |

|----------------------------------------------|------------------------|------------------|---------------------------|------------------|--------------------|

| VSEN Overvoltage Threshold                   | Factory setting        | -                | 115                       | -                | % V <sub>OUT</sub> |

|                                              | Configurable via PMBus | 0                | -                         | 115              | % V <sub>OUT</sub> |

| VSEN Undervoltage Hysteresis                 |                        | -                | 5                         | -                | % V <sub>OUT</sub> |

| VSEN Undervoltage/Overvoltage Fault Response | Factory setting        | -                | 16                        | -                | μs                 |

| ime                                          | Configurable via PMBus | 5                | -                         | 60               | μs                 |

| Thermal Protection Threshold                 | Factory setting        | -                | 125                       | -                | °C                 |

| (Controller Junction Temperature)            | Configurable via PMBus | -40              | -                         | 125              | °C                 |

| Thermal Protection Hysteresis                |                        | -                | 15                        | -                | °C                 |

#### NOTES:

- 10. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

- 11. Parameters with TYP limits are not production tested unless otherwise specified.

- 12. Parameters are 100% tested for internal controller prior to module assembly.

- 13.  $V_{OUT}$  measured at the termination of the FB+ and FB- sense points.

- 14. The device requires a delay period following an enable signal and prior to ramping its output.

- 15. Precise ramp timing mode is only valid when using the EN pin to enable the device rather than PMBus enable.

- 16. The devices may require up to a 4ms delay following the assertion of the enable signal (normal mode) or following the de-assertion of the enable signal.

- 17. Factory setting for Power-good delay is set to the same value as the soft-start ramp time.

- 18. Nominal capacitance of logic pins is 5pF.

- 19. Maximum duty cycle is limited by the equation MAX\_DUTY(%) = [1 (150×10<sup>-9</sup> × f<sub>SW</sub>)] × 100 and not to exceed 95%.

- 20. The load current is related to the thermal derating curves. The maximum allowed current is derated while the output voltage goes higher than 2.5V.

Submit Document Feedback 10 intersil FN8422.3 March 16, 2016

##

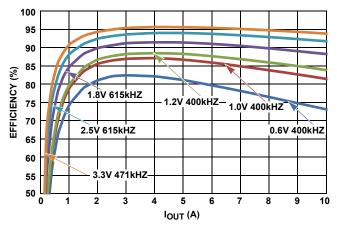

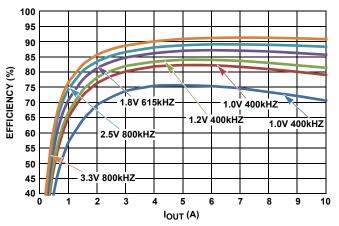

Typical values are used unless otherwise noted.

FIGURE 3. ZL9010M EFFICIENCY, VIN = 5V

FIGURE 4. ZL9010M EFFICIENCY, VIN = 12V

FIGURE 5. V<sub>OUT</sub> = 1.2V TRANSIENT RESPONSE

FIGURE 6. V<sub>OUT</sub> = 1.8V TRANSIENT RESPONSE

FIGURE 7. V<sub>OUT</sub> = 2.5V TRANSIENT RESPONSE

FIGURE 8.  $V_{OUT} = 3.3V$  TRANSIENT RESPONSE

### Typical Performance Curves Operating conditions: T<sub>A</sub> = +25 °C, No air flow, C<sub>OUT</sub> = 3 x 100 μF + 1 x 330 μF.

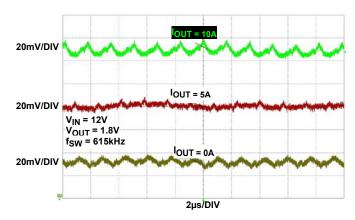

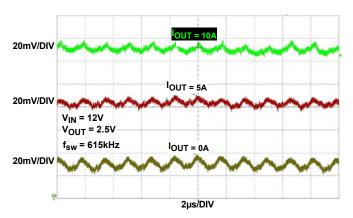

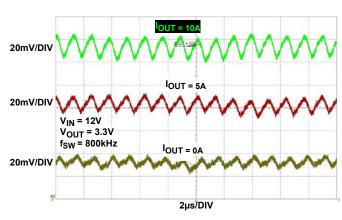

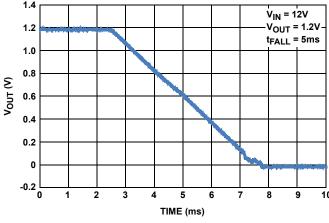

Typical values are used unless otherwise noted. (Continued)

FIGURE 9. V<sub>OUT</sub> = 1.2V OUTPUT VOLTAGE RIPPLE

FIGURE 10. V<sub>OUT</sub> = 1.8V OUTPUT VOLTAGE RIPPLE

FIGURE 11. V<sub>OUT</sub> = 2.5V OUTPUT VOLTAGE RIPPLE

FIGURE 12. V<sub>OUT</sub> = 3.3V OUTPUT VOLTAGE RIPPLE

FIGURE 13. SOFT-STOP RAMP-DOWN

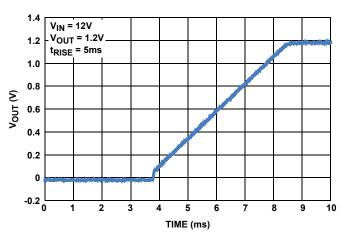

FIGURE 14. SOFT-START RAMP-UP

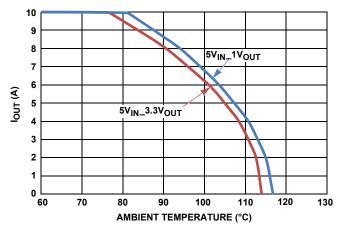

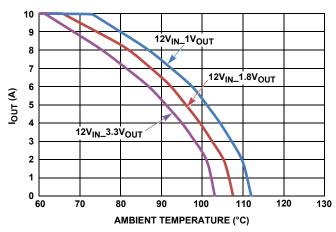

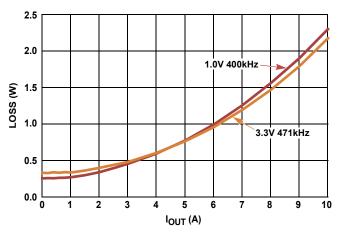

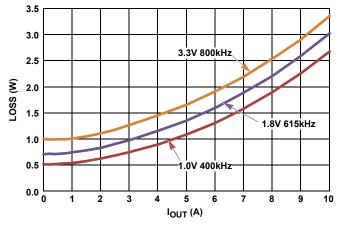

Submit Document Feedback 12 intersil FN8422.3 **Derating Curves** Operating conditions: T<sub>A</sub> = +25°C, No air flow. f<sub>SW</sub> corresponds to those used in Efficiency curves.  $C_{OUT}$  = 3 x 100 $\mu$ F + 1 x 330 $\mu$ F. Typical values are used unless otherwise noted.

FIGURE 15. DERATING CURVE, 5V<sub>IN</sub> FOR VARIOUS OUTPUT **VOLTAGES, NO AIR FLOW**

FIGURE 16. DERATING CURVE, 12VIN FOR VARIOUS OUTPUT **VOLTAGES, NO AIR FLOW**

FIGURE 17. POWER LOSS CURVE,  $5V_{\mbox{\footnotesize{IN}}}$  FOR VARIOUS OUTPUT **VOLTAGES**

FIGURE 18. POWER LOSS CURVE,  $12V_{\mbox{\scriptsize IN}}$  FOR VARIOUS OUTPUT **VOLTAGES**

13 intersil FN8422.3 March 16, 2016

FIGURE 19. TEST CIRCUIT FOR ALL PERFORMANCE AND DERATING CURVES

#### NOTES:

- 21. The PMBus requires pull-up resistors. Please refer to the PMBus specifications for more details.

- 22. The DDC bus requires a pull-up resistor. The resistance will vary based on the capacitive loading of the bus (and on the number of devices connected). The 10kΩ default value, assuming a maximum of 100pF per device, provides the necessary 1μs pull-up rise time. Please refer to "Digital-DC Bus" on page 24 for more details

- 23. Additional capacitance may be required to meet specific transient response targets.

### **Application Information**

### **Internal Bias and Input Voltage Considerations**

Beside VIN supplying the main power conversion, the ZL9010M employs two internal low dropout (LDO) regulators to supply bias voltages for internal circuitry allowing it to operate from a single input supply. The internal bias regulators are as indicated in the following:

VR - The VR LDO provides a regulated 5V bias supply for the MOSFET driver circuits. It is powered from the VDD pin.

**V25** - The V25 LDO provides a regulated 2.5V bias supply for the main controller circuitry. It is powered from an internal 5V node.

When the input supply (VDD) is higher than 5.5V, the VR pin should not be connected to any other pin. Due to the dropout voltage associated with the VR bias regulator, the VDD pin can be connected to the VR pin for designs operating from a supply below 5.5V. The internal bias regulators are not designed to be outputs for powering other circuitry, so keep current into the VDD pin below

Typically, VDD is connected directly to VIN. In the case that VDD is powered separately from VIN, the recommended power sequence is to keep EN low, power VDD and then VIN. When the voltage is applied to VIN, VDD should also be applied to avoid unintentional turn-on of the internal high-side MOSFET. If the VDD voltage is different from VIN, prebias start-up and auto-compensation may not work correctly as the VDD voltage is

used to measure input voltage as part of the Prebias and Auto-compensation calculation.

#### **Design Trade-Offs with Switching Frequency**

For design of the buck power stage, there is a trade-off when choosing switching frequency to achieve higher power supply efficiency, output ripple and transient response. For output voltages below 2V, a lower switching frequency results in higher efficiency. A lower output ripple and faster transient response is achieved with higher switching frequencies and thereby can reduce the required amount of output capacitance. Also, given an input to output voltage relation, there is a limitation on the allowable switching frequency due to normal part operation. See "Switching Frequency and PLL" on page 19 for more considerations.

To start the design with a goal of high efficiency, select a frequency based on Table 1. To achieve good transient response, a minimum switching frequency of 615kHz is recommended.

**TABLE 1. OPTIMAL SWITCHING FREQUENCY FOR EFFICIENCY**

| v <sub>o</sub> -v <sub>IN</sub> | 3.3V<br>(kHz) | 5V<br>(kHz) | 12V<br>(kHz) |

|---------------------------------|---------------|-------------|--------------|

| 0.6 - 1.5                       | 300           | 400         | 400          |

| 1.5 - 2.5                       | 300           | 615         | 615          |

| 2.5 - 3.6                       | 300           | 400         | 800          |

Submit Document Feedback FN8422.3 14 intersil

#### **Completing a Power Supply Design**

To achieve a power supply design with digital capabilities using ZL9010M, only input and output capacitors and two resistors are needed. The two resistors are installed on the SA and V1 pins for setting the PMBus address and output voltage, respectively.

#### **Selection of the Input Capacitor**

The input filter capacitor should be based on how much ripple the supply can tolerate on the DC input line. The larger the capacitor, the less ripple expected, but consideration should be taken for the higher surge current during power-up. The ZL9010M provides the soft-start function that controls and limits the current surge. The value of the input capacitor can be calculated by Equation 1:

$$C_{IN(MIN)} = I_O \bullet \frac{D \bullet (1-D)}{V_{P-P(MAX)} \bullet f_{SW}}$$

(EQ. 1)

#### Where:

$C_{IN(MIN)}$  is the minimum input capacitance (µF) required  $I_{O}$  is the output current (A)

D is the duty cycle  $(V_O/V_{IN})$

V<sub>P-P(MAX)</sub> is the maximum peak-to-peak voltage (V) f<sub>SW</sub> is the switching frequency (Hz)

In addition to the bulk capacitance, some low Equivalent Series Resistance (ESR) ceramic capacitance should be placed as close as possible to decouple between the drain terminal of the high-side MOSFET (VIN PAD1) and the source terminal of the low-side MOSFET (PGND PAD2). This is used to reduce voltage ringing created by the switching current across parasitic circuit elements. This ripple's (I<sub>CINrms</sub>) impact should be considered and can be determined from Equation 2:

$$I_{CINrms} = I_{OUT} \times \sqrt{D \times (1 - D)}$$

(EQ. 2)

Without capacitive filtering near the power supply circuit, this current would flow through the supply bus and return planes, coupling noise into other system circuitry. The input capacitors should be rated at 1.2x the ripple current calculated in <a href="Equation 2">Equation 2</a> to avoid overheating of the capacitors due to the high ripple current, which can cause premature failure.

#### **Selection of the Output Capacitors**

The ZL9010M is designed for low output voltage ripple. The output voltage ripple and transient requirements can be met with bulk output capacitors ( $C_{OUT}$ ) with low ESR; the recommended minimum ESR is <6M $\Omega$ .  $C_{OUT}$  can be a low ESR tantalum capacitor, a low ESR polymer capacitor or a ceramic capacitor.

The typical output capacitance range is from 200 $\mu$ F to 1200 $\mu$ F and decoupling ceramic output capacitors are used per phase. The optimized output capacitance is 700 $\mu$ F with an ESR of 5m $\Omega$ . The maximum recommended product of output capacitance and equivalent ESR value is given by [C<sub>OUT</sub> x ESR] <3600 ( $\mu$ F x m $\Omega$ ).

With a step load faster than  $0.2A/\mu s$ , the recommended amount of output capacitor is  $100\mu F$  per ampere of step load. Additional output filtering may be needed if further reduction of output ripple or dynamic transient spikes are required.

### **Functional Description**

#### **Multi-Mode Pins**

In order to simplify circuit design, the ZL9010M family incorporates patented multi-mode pins that allow the user to easily configure many aspects of the device without programming. Most power management features can be configured using these pins. The multi-mode pins can respond to two types of configurations summarized in <a href="Table 2">Table 2</a>. These pins are sampled when power is applied or by issuing a PMBus command RESTORE\_FACTORY\_ALL. Refer to <a href="PMBus Command Summary" on page 29">"PMBus Command Summary" on page 29</a>.

Pin-strap Settings: With pin strapping, parameters can be set by strapping the pins in one of three possible states: LOW, OPEN, or HIGH. These pins can be connected to SGND for logic LOW as this pin provides a voltage lower than 0.8V. For logic OPEN, they have no connection. These pins can be connected to the V25 pin for logic HIGH settings as this pin provides a regulated voltage higher than 2V when power is applied to the VDD pin.

Resistor Settings: Allows a greater range of adjustability when connecting a finite value resistor (in a specified range) between the multi-mode pin and SGND. Standard 1% resistor values are used and only every fourth standard resistor value is used so the device can reliably recognize the value of resistance connected to the pin while eliminating the error associated with the resistor accuracy. Up to 31 unique selections are available using a single resistor.

**TABLE 2. MULTI-MODE PIN CONFIGURATION**

| PIN TIED TO       | VALUE                 |

|-------------------|-----------------------|

| LOW (Logic LOW)   | <0.8VDC               |

| OPEN (N/C)        | No connection         |

| HIGH (Logic HIGH) | >2.0VDC               |

| Resistor to SGND  | Set by resistor value |

There are five multi-mode pins in ZL9010M: FC0, SA, SYNC, SS and V1. The multi-mode pin configuration can set ZL9010M power management features and mode of operation to both single-phase and current-sharing without any programming. SA and V1 are the only two pins that must be set for a general single-phase operation, which use the default settings associated with the other three pins, or overriding other parameters via the PMBus.

The SA sets the PMBus address, phase spreading and Reference/Member assignment in current sharing mode. The effective phase spreading depends on the mode of operation. The Reference/Member is pre-assigned in current sharing mode and up to 8 two-phase with 5 three-phase current-shared group is possible.

The FC0 is used to distinguish between the two modes of operation and is used in combination with SA in current sharing mode. FC0 pin strapping and resistor programming in the range of  $10k\Omega$  to  $42.2k\Omega$  set the operation to single-phase mode, while the range of  $46.4k\Omega$  to  $178k\Omega$  is for current sharing mode. The FC0 also sets the Autocomp and Sync configuration.

Submit Document Feedback 15 intersil FN8422.3

The SYNC sets the switching frequency and is only effective in single-phase mode, as SYNC pins are connected together in current-sharing mode.

The SS sets the ramp timing, UVLO and tracking. The V1 sets the output voltage. The SS and V1 are the same purpose in single-phase and current-share modes.

#### **PMBus Communications**

The ZL9010M provides an PMBus digital interface that enables the user to configure all aspects of the module operation as well as monitor the input and output parameters. The ZL9010M can be used with any PMBus host device. In addition, the module is compatible with PMBus version 2.0 and includes a SALRT line to help mitigate bandwidth limitations related to continuous fault monitoring. Pull-up resistors are required on the PMBus as specified in the PMBus 2.0 specification. The ZL9010M accepts most standard PMBus commands. When controlling the device with PMBus commands, it is recommended that the enable pin be tied to SGND.

The PMBus device address and VOUT\_MAX are the only parameters that must be set by external pins. All other device parameters can be set via the PMBus. The device address is set using the SA pin. VOUT\_MAX is determined as 10% greater than the voltage set by the V1 pin.

The ZL9010M supports 100kHz and 400kHz PMBus clock speed with communication interval of 20ms between STORE and RESTORE commands and ~2ms for other general commands.

#### **PMBus Module Address Selection**

Each module must have its own unique serial address to distinguish between other devices on the bus. The module address is set by connecting a resistor between the SA pin and SGND. Table 3 lists the available module addresses.

**TABLE 3. PMBus ADDRESS VALUES**

| R <sub>SA</sub> (kΩ) | PMBus ADDRESS |

|----------------------|---------------|

| LOW                  | 0x23          |

| OPEN                 | 0x24          |

| HIGH                 | 0x25          |

| 10                   | 0x50          |

| 11                   | 0x51          |

| 12.1                 | 0x52          |

| 13.3                 | 0x53          |

| 14.7                 | 0x54          |

| 16.2                 | 0x55          |

| 17.8                 | 0x56          |

| 19.6                 | 0x57          |

| 21.5                 | 0x58          |

| 23.7                 | 0x59          |

| 26.1                 | 0x5A          |

| 28.7                 | 0x5B          |

| 31.6                 | 0x5C          |

TABLE 3. PMBus ADDRESS VALUES (Continued)

| R <sub>SA</sub> (kΩ) | PMBus ADDRESS |

|----------------------|---------------|

| 34.8                 | 0x5D          |

| 38.3                 | 0x5E          |

| 42.2                 | 0x5F          |

| 46.4                 | 0x60          |

| 51.1                 | 0x61          |

| 56.2                 | 0x62          |

| 61.9                 | 0x63          |

| 68.1                 | 0x64          |

| 75                   | 0x65          |

| 82.5                 | 0x66          |

| 90.9                 | 0x67          |

| 100                  | 0x68          |

| 110                  | 0x69          |

| 121                  | 0x6A          |

| 133                  | 0x6B          |

| 147                  | 0x6C          |

| 162                  | 0x6D          |

| 178                  | 0x6E          |

### **Phase Spreading for a Single-Phase Mode of Operation**

When multiple point-of-load converters share a common DC input supply, it is desirable to adjust the clock phase offset of each device such that not all devices start to switch simultaneously. Setting each converter to start its switching cycle at a different point in time can dramatically reduce input capacitance requirements and efficiency losses. Since the peak current drawn from the input supply is effectively spread out over a period of time, the peak current drawn at any given moment is reduced and the power losses proportional to the I<sub>RMS</sub><sup>2</sup> are reduced dramatically.

To enable spreading, all converters must be synchronized to the same switching clock. The FCO pin is used to set the configuration of the SYNC pin for each device as described in "Switching Frequency and PLL" on page 19.

Selecting the phase offset for the device in a standalone mode of operation is accomplished by selecting a device address according to the Equation 3:

Phase Offset= device address

$$\times$$

45° (EQ. 3)

#### For example:

- A device address of 0x50 or 0x60 would configure no phase

- A device address of 0x51 or 0x61 would configure 45° of phase offset

- A device address of 0x52 or 0x62 would configure 90° of phase offset

Submit Document Feedback intersil FN8422.3 16

The phase offset of each device may also be set to any value between 0° and 360° in 22.5° increments via the PMBus interface. Refer to "PMBus Command Summary" on page 29 for further details.

#### **Output Voltage Selection**

The output voltage may be set to a voltage between 0.6V and 3.6V provided that the input voltage is higher than the desired output voltage by an amount sufficient to prevent the device from exceeding its maximum duty cycle specification.

The V1 pins are used to set the output voltage using a single resistor, R<sub>SET</sub> between the V1 pins and SGND. Table 4 lists the available output voltage settings with a single resistor.

TABLE 4. SINGLE RESISTOR VOUT SETTING

| R <sub>SET</sub> (kΩ) | V <sub>OUT</sub> |

|-----------------------|------------------|

| LOW                   | 1.20             |

| OPEN                  | 1.50             |

| HIGH                  | 3.30             |

| 10                    | 0.60             |

| 11                    | 0.65             |

| 12.1                  | 0.70             |

| 13.3                  | 0.75             |

| 14.7                  | 0.80             |

| 16.2                  | 0.85             |

| 17.8                  | 0.90             |

| 19.6                  | 0.95             |

| 21.5                  | 1.00             |

| 23.7                  | 1.05             |

| 26.1                  | 1.10             |

| 28.7                  | 1.15             |

| 31.6                  | 1.20             |

| 34.8                  | 1.25             |

| 38.3                  | 1.30             |

| 42.2                  | 1.40             |

| 46.4                  | 1.50             |

| 51.1                  | 1.60             |

| 56.2                  | 1.70             |

| 61.9                  | 1.80             |

| 68.1                  | 1.90             |

| 75                    | 2.00             |

| 82.5                  | 2.10             |

| 90.9                  | 2.20             |

| 100                   | 2.30             |

| 110                   | 2.50             |

TABLE 4. SINGLE RESISTOR VOUT SETTING (Continued)

| R <sub>SET</sub> (kΩ) | V <sub>OUT</sub> |

|-----------------------|------------------|

| 121                   | 2.80             |

| 133                   | 3.00             |

| 147                   | 3.30             |

| 162                   | 3.60             |

The output voltage may also be set to any value between 0.6V and 3.6V using a PMBus command over the PMBus interface. Refer to "PMBus Command Summary" on page 29.

The R<sub>SET</sub> resistors program places an upper limit in output voltage setting through PMBus programming to 10% above the value set by the resistors.

#### Start-Up Procedure

The ZL9010M follows a specific internal start-up procedure after power is applied to the VDD pin. Table 5 describes the start-up sequence.

If the device is to be synchronized to an external clock source, the clock frequency must be stable prior to asserting the EN pin. The device requires approximately 5ms to 6ms to check for specific values stored in its internal memory. If the user has stored values in memory, those values will be loaded. The device will then check the status of all multi-mode pins and load the values associated with the pin settings.

Once this process is completed, the device is ready to accept commands via the PMBus interface and the device is ready to be enabled. Once enabled, the device requires a minimum delay period following an enable signal and prior to ramping its output, as described in "Soft-Start Delay and Ramp Times" on page 18. If a soft-start delay period less than the minimum has been configured (using PMBus commands), the device will default to the minimum delay period. If a delay period greater than the minimum is configured, the device will wait for the configured delay period prior to starting to ramp its output.

After the delay period has expired, the output will begin to ramp towards its target voltage according to the preconfigured soft-start ramp time that has been set using the SS pin. It should be noted that if the EN pin is tied to VDD, the device will still require approximately 5ms to 6ms before the output can begin its ramp-up as described in Table 5 on page 18.

Submit Document Feedback intersil FN8422.3 17 March 16, 2016

**TABLE 5. ZL9010M START-UP SEQUENCE**

| STEP# | STEP NAME             | DESCRIPTION                                                                                                                                                                 | TIME DURATION                                          |

|-------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| 1     | Power Applied         | Input voltage is applied to the ZL9010M's VDD pin.                                                                                                                          | Depends on input supply ramp time                      |

| 2     | Internal Memory Check | The device will check for values stored in its internal memory. This step is also performed after a Restore command.                                                        | Approximately 5ms to 6ms (device will ignore an enable |

| 3     | Multi-mode Pin Check  | The device loads values configured by the multi-mode pins.                                                                                                                  | signal or PMBus traffic during this<br>period)         |

| 4     | Device Ready          | The device is ready to accept an enable signal.                                                                                                                             |                                                        |

| 5     | Pre-ramp Delay        | The device requires a minimum delay period following an enable signal and prior to ramping its output, as described in <u>"Soft-Start Delay and Ramp Times"</u> on page 18. |                                                        |

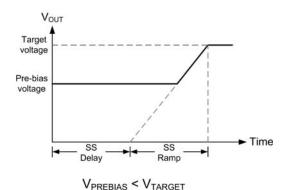

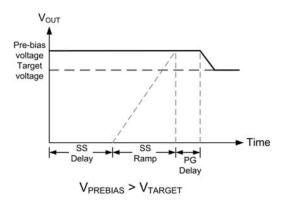

#### **Soft-Start Delay and Ramp Times**

It may be necessary to set a delay when an enable signal is received until the output voltage starts to ramp to its target value. In addition, the designer may wish to precisely set the time required for V<sub>OUT</sub> to ramp to its target value after the delay period has expired. These features may be used as part of an overall inrush current management strategy or to precisely control how fast a load IC is turned on. The ZL9010M gives the system designer several options for precisely and independently controlling both the delay and ramp time periods.

The soft-start delay period begins when the EN pin is asserted and ends when the delay time expires. The soft-start ramp timer enables a precisely controlled ramp to the nominal V<sub>OUT</sub> value that begins once the delay period has expired. The ramp-up is guaranteed monotonic and its slope may be precisely set using the SS pin.

The soft-start delay and ramp times can be set to a custom value by pin-strapping or connecting a resistor from the SS pin to SGND using the appropriate resistor value from Table 6. See "Input Undervoltage Lockout" on page 21 for further explanation of UVLO setting using SS pin. The value of this resistor is measured upon start-up or Restore and will not change if the resistor is varied after power has been applied to the ZL9010M.

TABLE 6. SOFT-START PIN-STRAP/RESISTOR SETTINGS

| R <sub>SS</sub><br>(kΩ) | DELAY TIME<br>(ms) | RAMP TIME<br>(ms) | UVLO<br>(V) |

|-------------------------|--------------------|-------------------|-------------|

| LOW                     | 5                  | 2                 | 4.5         |

| OPEN                    | 5                  | 5                 |             |

| HIGH                    | 10                 | 10                |             |

| 10                      | 5                  | 2                 | 3           |

| 11                      | 5                  | 5                 |             |

| 12.1                    | 10                 |                   |             |

| 13.3                    | 20                 |                   |             |

| 14.7                    | 5                  | 10                |             |

| 16.2                    | 10                 |                   |             |

| 17.8                    | 20                 |                   |             |

TABLE 6. SOFT-START PIN-STRAP/RESISTOR SETTINGS (Continued)

| R <sub>SS</sub><br>(kΩ) | DELAY TIME<br>(ms) | RAMP TIME<br>(ms) | UVLO<br>(V) |  |

|-------------------------|--------------------|-------------------|-------------|--|

| 19.6                    | 5                  | 2                 | 4.5         |  |

| 21.5                    | 10                 |                   |             |  |

| 23.7                    | 5                  | 5                 |             |  |

| 26.1                    | 10                 |                   |             |  |

| 28.7                    | 20                 |                   |             |  |

| 31.6                    | 5                  | 10                |             |  |

| 34.8                    | 10                 |                   |             |  |

| 38.3                    | 20                 |                   |             |  |

| 42.2                    | 5                  | 2                 | 10.8        |  |

| 46.4                    | 10                 |                   |             |  |

| 51.1                    | 5                  | 5                 |             |  |

| 56.2                    | 10                 |                   |             |  |

| 61.9                    | 20                 |                   |             |  |

| 68.1                    | 5                  | 10                |             |  |

| 75                      | 10                 |                   |             |  |

| 82.5                    | 20                 |                   |             |  |

With the SS pin OPEN, the default value for delay time and ramp time is 5ms. The soft-start delay and ramp times are set to custom values via the PMBus interface. When the delay time is set to 0ms, the device begins its ramp-up after the internal circuitry has initialized (approximately 2ms). When the soft-start ramp period is set to 0ms, the output ramps up as quickly as the output load capacitance and loop settings allow. It is generally recommended to set the soft-start ramp to a value greater than 500µs to prevent inadvertent fault conditions due to excessive inrush current.

The ZL9010M has a minimum  $t_{\mbox{ON\_DELAY}}$  requirement that is a function of the operating mode. Table 7 shows the different mode configurations and the minimum  $t_{\mbox{ON}}$  DELAY required for each mode. Current sharing is configured with the ISHARE\_CONFIG PMBus command, Auto compensation is configured with the AUTO\_COMP\_CONFIG command and standby mode is configured as low power with the USER\_CONFIG command. Refer to "PMBus Command Summary" on page 29.

Submit Document Feedback FN8422.3 18 intersil

Resistor programming on the SS pin with a delay time of 20ms can be used to satisfy the minimum  $t_{\mbox{\scriptsize ON}}$  DELAY of 15ms.

TABLE 7. MINIMUM ton DELAY vs OPERATING MODE

| CURRENT<br>SHARING | AUTOCOMP | LOW-POWER<br>STANDBY | MIN.<br>t <sub>ON_DELAY</sub><br>(ms) |

|--------------------|----------|----------------------|---------------------------------------|

| Х                  | Disabled | False                | 5                                     |

| Disabled           | Enabled  | False                | 5                                     |

| Disabled           | Х        | True                 | 10                                    |

| Enabled            | Disabled | True                 | 15                                    |

| Enabled            | Enabled  | Х                    | 15                                    |

#### **Power-Good**

The ZL9010M provides a Power-good (PG) signal that indicates the output voltage is within a specified tolerance of its target level and no fault condition exists. By default, the PG pin asserts if the output is within +15/-10% of the target voltage. These limits and the polarity of the pin may be changed via the PMBus interface. Refer to "PMBus Command Summary" on page 29.

A PG delay period is defined as the time when all conditions within the ZL9010M for asserting PG are met, to when the PG pin is actually asserted. This feature is commonly used instead of using an external reset controller to control external digital logic.

By default, the ZL9010M PG delay is set to 1ms and may be changed using the PMBus as described in "PMBus Command Summary" on page 29.

By default, the ZL9010M PG delay is set equal to the soft-start ramp time setting. Therefore, if the soft-start ramp time is set to 6ms, the PG delay is set to 6ms. The PG delay may be set independently of the soft-start ramp using the PMBus as described in "PMBus Command Summary" on page 29.

If Auto Comp is enabled, the PG timing is further controlled by the PG Assert parameter, as described in "Loop Compensation" on page 20.

#### **Switching Frequency and PLL**

The ZL9010M incorporates an internal phase-locked loop (PLL) to clock the internal circuitry. The PLL can be driven by an external clock source connected to the SYNC pin. When using the internal oscillator, the SYNC pin can be configured as a clock source for other Intersil Digital devices. With the FCO pin, the SYNC pin can be configured as input, Auto detect and Output. Pinstrap resistor setting to "input" mode is applicable for member devices used in current sharing mode only.

When multiple modules are used together, connecting the SYNC pins together will force all devices to synchronize with each other. One device must set its SYNC pin as an output and the remaining devices must have their SYNC pins set as Auto Detect.

#### **SYNC AUTO DETECT**

In Auto Detect mode, the module will check for a clock signal on the SYNC pin immediately after power-up. In this case, the incoming clock signal must be in the range of 300kHz to 1.0MHz and must be stable within 10µs after V25 rises above 2.25V. If

the device is in Low Power Mode, it will check for a clock signal on the SYNC pin immediately after EN goes true. In this case, the incoming clock signal must be in range and stable before EN goes true. If a clock signal is present, the ZL9010M's oscillator will then synchronize with the rising edge of the external clock.

If no incoming clock signal is present, the ZL9010M will configure the switching frequency according to an external resistor, R<sub>SYNC</sub>, connected between SYNC and SGND using Table 8, given that FCO used pin-strap or has a resistor R<sub>FCO</sub> in the range of  $10k\Omega$  to  $13.3k\Omega$ . When FCO is OPEN, or used with resistor settings in the range, the switching frequency of the ZL9010M is set to a default of 615kHz. The module will only read the SYNC pin connection during the first start-up sequence; changes to SYNC pin connections will not affect f<sub>SW</sub> until the power (V<sub>DD</sub>) is cycled off and on. Frequency modifications without restarting the VDD power can disable the SYNC auto detect function.

#### **SYNC OUTPUT**

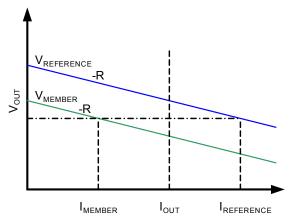

When the SYNC pin is configured as an output via PMBus, the device will run from its internal oscillator and will drive the resulting internal oscillator signal onto the SYNC pin so other devices can be synchronized to it. The SYNC pin will not be checked for an incoming clock signal while in this mode.